Logic optimization

Logic optimization, a part of logic synthesis in electronics, is the process of finding an equivalent representation of the specified logic circuit under one or more specified constraints. Generally the circuit is constrained to minimum chip area meeting a prespecified delay.

Contents

Introduction[edit]

With the advent of logic synthesis, one of the biggest challenges faced by the electronic design automation (EDA) industry was to find the best netlist representation of the given design description. While two-level logic optimization had long existed in the form of the Quine–McCluskey algorithm, later followed by the Espresso heuristic logic minimizer, the rapidly improving chip densities, and the wide adoption of HDLs for circuit description, formalized the logic optimization domain as it exists today.

Today, logic optimization is divided into various categories:

Based on circuit representation

- Two-level logic optimization

- Multi-level logic optimization

Based on circuit characteristics

- Sequential logic optimization

- Combinational logic optimization

Based on type of execution

- Graphical optimization methods

- Tabular optimization methods

- Algebraic optimization methods

While a two-level circuit representation of circuits strictly refers to the flattened view of the circuit in terms of SOPs (sum-of-products) — which is more applicable to a PLA implementation of the design[clarification needed] — a multi-level representation is a more generic view of the circuit in terms of arbitrarily connected SOPs, POSs (product-of-sums), factored form etc. Logic optimization algorithms generally work either on the structural (SOPs, factored form) or functional (BDDs, ADDs) representation of the circuit.[clarification needed]

Two-level versus multi-level representations[edit]

If we have two functions F1 and F2:

The above 2-level representation takes six product terms and 24 transistors in CMOS Rep.[why?]

A functionally equivalent representation in multilevel can be:

- P = B + C.

- F1 = AP + AD.

- F2 = A'P + A'E.

While the number of levels here is 3, the total number of product terms and literals reduce[quantify] because of the sharing of the term B + C.

Similarly, we distinguish between sequential and combinational circuits, whose behavior can be described in terms of finite-state machine state tables/diagrams or by Boolean functions and relations respectively.[clarification needed]

Circuit minimization in Boolean algebra[edit]

In Boolean algebra, circuit minimization is the problem of obtaining the smallest logic circuit (Boolean formula) that represents a given Boolean function or truth table. For the case when the boolean function is specified by a circuit (that is, we want to find an equivalent circuit of minimum size possible), the unbounded circuit minimization problem was long-conjectured to be -complete, a result finally proved in 2008,[1] but there are effective heuristics such as Karnaugh maps and the Quine–McCluskey algorithm that facilitate the process.

Purpose[edit]

The problem with having a complicated circuit (i.e. one with many elements, such as logic gates) is that each element takes up physical space in its implementation and costs time and money to produce in itself. Circuit minimization may be one form of logic optimization used to reduce the area of complex logic in integrated circuits.

Example[edit]

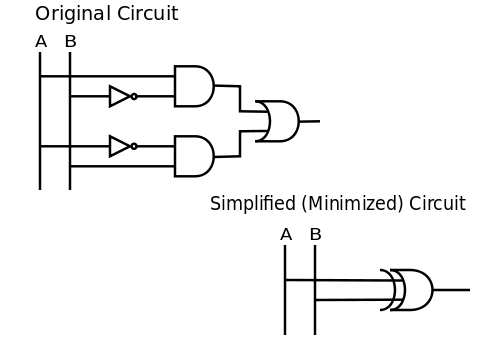

While there are many ways to minimize a circuit, this is an example that minimizes (or simplifies) a boolean function. Note that the boolean function carried out by the circuit is directly related to the algebraic expression from which the function is implemented.[2] Consider the circuit used to represent . It is evident that two negations, two conjunctions, and a disjunction are used in this statement. This means that to build the circuit one would need two inverters, two AND gates, and an OR gate.

We can simplify (minimize) the circuit by applying logical identities or using intuition. Since the example states that A is true when B is false or the other way around, we can conclude that this simply means . In terms of logical gates, inequality simply means an XOR gate (exclusive or). Therefore, . Then the two circuits shown below are equivalent:

You can additionally check the correctness of the result using a truth table.

Graphical two-level logic minimization methods[edit]

Graphical minimization methods for two-level logic include:

- Marquand diagram (1881) by Allan Marquand (1853–1924)[3][4]

- Harvard minimizing chart (1951) by Howard H. Aiken and Martha L. Whitehouse of the Harvard Computation Laboratory[5][6][7][8]

- Veitch chart (1952) by Edward Veitch (1924–2013)[9][4]

- Karnaugh map (1953) by Maurice Karnaugh (1924–)[6][8]

- Svoboda's graphical aids (1956) and triadic map by Antonín Svoboda (1907–1980)[10][11][12][13]

- Händler circle graph (aka Händler'scher Kreisgraph, Kreisgraph nach Händler, Händler-Kreisgraph, Händler-Diagramm, Minimisierungsgraph [sic]) (1958) by Wolfgang Händler (1920–1998)[14][15][16][12][17][18][19][20][21]

- Graph method (1965) by Herbert Kortum (1907–1979)[22][23][24][25][26][27][28]

See also[edit]

- Binary decision diagram

- Circuit minimization

- Espresso heuristic logic minimizer

- Karnaugh map

- Petrick's method

- Prime implicant

- Circuit complexity

- Function composition

- Function decomposition

- Gate underutilization

References[edit]

- ^ Buchfuhrer, David; Umans, Christopher (January 2011). "The complexity of Boolean formula minimization" (PDF). Journal of Computer and System Sciences (JCSS). 77 (1): 142–153. doi:10.1016/j.jcss.2010.06.011. This is an extended version of the conference paper: Buchfuhrer, David; Umans, Christopher (2008). "The Complexity of Boolean Formula Minimization" (PDF). Written at 35th International Colloquium (ICALP). Proceedings of Automata, Languages and Programming. Lecture Notes in Computer Science (LNCS). 5125. Berlin / Heidelberg, Germany: Springer-Verlag. pp. 24–35. doi:10.1007/978-3-540-70575-8_3. ISBN 978-3-540-70574-1. Archived (PDF) from the original on 2018-01-14. Retrieved 2018-01-14.

- ^ Mano, M. Morris; Kime, Charles R. (2014). Logic and Computer Design Fundamentals (4th new international ed.). Pearson Education Limited. p. 54. ISBN 978-1-292-02468-4.

- ^ Marquand, Allan (1881). "XXXIII: On Logical Diagrams for n terms". The London, Edinburgh, and Dublin Philosophical Magazine and Journal of Science. 5. 12 (75): 266–270. doi:10.1080/14786448108627104. (NB. Quite many secondary sources erroneously cite this work as "A logical diagram for n terms" or "On a logical diagram for n terms".)

- ^ a b Brown, Frank Markham (2012) [2003, 1990]. Boolean Reasoning - The Logic of Boolean Equations (reissue of 2nd ed.). Mineola, New York: Dover Publications, Inc. ISBN 978-0-486-42785-0. [1]

- ^ Aiken, Howard H.; Blaauw, Gerrit; Burkhart, William; Burns, Robert J.; Cali, Lloyd; Canepa, Michele; Ciampa, Carmela M.; Coolidge, Jr., Charles A.; Fucarile, Joseph R.; Gadd, Jr., J. Orten; Gucker, Frank F.; Harr, John A.; Hawkins, Robert L.; Hayes, Miles V.; Hofheimer, Richard; Hulme, William F.; Jennings, Betty L.; Johnson, Stanley A.; Kalin, Theodore; Kincaid, Marshall; Lucchini, E. Edward; Minty, William; Moore, Benjamin L.; Remmes, Joseph; Rinn, Robert J.; Roche, John W.; Sanbord, Jacquelin; Semon, Warren L.; Singer, Theodore; Smith, Dexter; Smith, Leonard; Strong, Peter F.; Thomas, Helene V.; Wang, An; Whitehouse, Martha L.; Wilkins, Holly B.; Wilkins, Robert E.; Woo, Way Dong; Little, Elbert P.; McDowell, M. Scudder (1952) [January 1951]. "Chapter V: Minimizing charts". Synthesis of electronic computing and control circuits (second printing, revised ed.). Write-Patterson Air Force Base: Harvard University Press (Cambridge, Massachusetts, USA) / Geoffrey Cumberlege Oxford University Press (London). pp. preface, 50–67. Retrieved 2017-04-16.

[…] Martha Whitehouse constructed the minimizing charts used so profusely throughout this book, and in addition prepared minimizing charts of seven and eight variables for experimental purposes. […] Hence, the present writer is obliged to record that the general algebraic approach, the switching function, the vacuum-tube operator, and the minimizing chart are his proposals, and that he is responsible for their inclusion herein. […]

(NB. Work commenced in April 1948.) - ^ a b Karnaugh, Maurice (November 1953) [1953-04-23, 1953-03-17]. "The Map Method for Synthesis of Combinational Logic Circuits" (PDF). Transactions of the American Institute of Electrical Engineers Part I. 72 (9): 593–599. doi:10.1109/TCE.1953.6371932. Paper 53-217. Archived (PDF) from the original on 2017-04-16. Retrieved 2017-04-16. (NB. Also contains a short review by Samuel H. Caldwell.)

- ^ Phister, Jr., Montgomery (1959) [December 1958]. Logical design of digital computers. New York, USA: John Wiley & Sons Inc. pp. 75–83. ISBN 0471688053.

- ^ a b Curtis, H. Allen (1962). A new approach to the design of switching circuits. The Bell Laboratories Series. Princeton, New Jersey, USA: D. van Nostrand Company, Inc.

- ^ Veitch, Edward W. (1952-05-03) [1952-05-02]. "A Chart Method for Simplifying Truth Functions". ACM Annual Conference/Annual Meeting: Proceedings of the 1952 ACM Annual Meeting (Pittsburg): 127–133. doi:10.1145/609784.609801.

- ^ Svoboda, Antonín (1956). "Graficko-mechanické pomůcky užívané při analyse a synthese kontaktových obvodů" [Utilization of graphical-mechanical aids for the analysis and synthesis of contact circuits]. Stroje na zpracování informací [Symphosium IV on information processing machines] (in Czech). IV: 9–21.

- ^ Svoboda, Antonín (1956). "Graphical Mechanical Aids for the Synthesis of Relay Circuits". Nachrichtentechnische Fachberichte (NTF), Beihefte der Nachrichtentechnischen Zeitschrift (NTZ).

- ^ a b Steinbuch, Karl W.; Weber, Wolfgang; Heinemann, Traute, eds. (1974) [1967]. Taschenbuch der Informatik - Band II - Struktur und Programmierung von EDV-Systemen. Taschenbuch der Nachrichtenverarbeitung (in German). 2 (3 ed.). Berlin, Germany: Springer-Verlag. pp. 25, 62, 96, 122–123, 238. ISBN 978-3-540-06241-7. LCCN 73-80607.

- ^ Svoboda, Antonín; White, Donnamaie E. (2016) [1979-08-01]. Advanced Logical Circuit Design Techniques (PDF) (retyped electronic reissue ed.). Garland STPM Press (original issue) / WhitePubs (reissue). ISBN 0-8240-7014-3. ISBN 978-0-8240-7014-4. Archived (PDF) from the original on 2016-03-15. Retrieved 2017-04-15. [2] [3]

- ^ Händler, Wolfgang (1958). Ein Minimisierungsverfahren zur Synthese von Schaltkreisen (Minimisierungsgraphen) (Dissertation) (in German). Technische Hochschule Darmstadt. D 17. [4] (NB. Although written by a German, the title contains an anglicism; the correct German term would be "Minimierung" instead of "Minimisierung".)

- ^ Händler, Wolfgang (2013) [1961]. "Zum Gebrauch von Graphen in der Schaltkreis- und Schaltwerktheorie". In Peschl, Ernst Ferdinand; Unger, Heinz. Colloquium über Schaltkreis- und Schaltwerk-Theorie - Vortragsauszüge vom 26. bis 28. Oktober 1960 in Bonn - Band 3 von Internationale Schriftenreihe zur Numerischen Mathematik [International Series of Numerical Mathematics] (ISNM) (in German). 3. Institut für Angewandte Mathematik, Universität Saarbrücken, Rheinisch-Westfälisches Institut für Instrumentelle Mathematik: Springer Basel AG / Birkhäuser Verlag Basel. pp. 169–198. doi:10.1007/978-3-0348-5770-3. ISBN 978-3-0348-5771-0. [5]

- ^ Berger, Erich R.; Händler, Wolfgang (1967) [1962]. Steinbuch, Karl W.; Wagner, Siegfried W., eds. Taschenbuch der Nachrichtenverarbeitung (in German) (2 ed.). Berlin, Germany: Springer-Verlag OHG. pp. 64, 1034–1035, 1036, 1038. LCCN 67-21079. Title No. 1036.

[…] Übersichtlich ist die Darstellung nach Händler, die sämtliche Punkte, numeriert nach dem Gray-Code […], auf dem Umfeld eines Kreises anordnet. Sie erfordert allerdings sehr viel Platz. […] [Händler's illustration, where all points, numbered according to the Gray code, are arranged on the circumference of a circle, is easily comprehensible. It needs, however, a lot of space.]

- ^ Hotz, Günter (1974). Schaltkreistheorie [Switching circuit theory]. DeGruyter Lehrbuch (in German). Walter de Gruyter & Co. p. 117. ISBN 978-3-11-00-2050-2.

[…] Der Kreisgraph von Händler ist für das Auffinden von Primimplikanten gut brauchbar. Er hat den Nachteil, daß er schwierig zu zeichnen ist. Diesen Nachteil kann man allerdings durch die Verwendung von Schablonen verringern. […] [The circle graph by Händler is well suited to find prime implicants. A disadvantage is that it is difficult to draw. This can be remedied using stencils.]

- ^ "Informatik Sammlung Erlangen (ISER)" (in German). Erlangen, Germany: Friedrich-Alexander Universität. 2012-03-13. Archived from the original on 2017-05-16. Retrieved 2017-04-12. (NB. Shows a picture of a Kreisgraph by Händler.)

- ^ "Informatik Sammlung Erlangen (ISER) - Impressum" (in German). Erlangen, Germany: Friedrich-Alexander Universität. 2012-03-13. Archived from the original on 2012-02-26. Retrieved 2017-04-15. (NB. Shows a picture of a Kreisgraph by Händler.)

- ^ Zemanek, Heinz (2013) [1990]. "Geschichte der Schaltalgebra" [History of circuit switching algebra]. In Broy, Manfred. Informatik und Mathematik [Computer Sciences and Mathematics] (in German). Springer-Verlag. pp. 43–72. ISBN 9783642766770.

Einen Weg besonderer Art, der damals zu wenig beachtet wurde, wies W. Händler in seiner Dissertation […] mit einem Kreisdiagramm. […]

[6] (NB. Collection of papers at a colloquium held at the Bayerische Akademie der Wissenschaften, 1989-06-12/14, in honor of Friedrich L. Bauer.) - ^ Bauer, Friedrich Ludwig; Wirsing, Martin (March 1991). Elementare Aussagenlogik (in German). Berlin / Heidelberg: Springer-Verlag. pp. 54–56, 71, 112–113, 138–139. ISBN 978-3-540-52974-3.

[…] handelt es sich um ein Händler-Diagramm […], mit den Würfelecken als Ecken eines 2m-gons. […] Abb. […] zeigt auch Gegenstücke für andere Dimensionen. Durch waagerechte Linien sind dabei Tupel verbunden, die sich nur in der ersten Komponente unterscheiden; durch senkrechte Linien solche, die sich nur in der zweiten Komponente unterscheiden; durch 45°-Linien und 135°-Linien solche, die sich nur in der dritten Komponente unterscheiden usw. Als Nachteil der Händler-Diagramme wird angeführt, daß sie viel Platz beanspruchen. […]

- ^ Kortum, Herbert (1965). "Minimierung von Kontaktschaltungen durch Kombination von Kürzungsverfahren und Graphenmethoden" [Minimization of contact circuits by combination of reduction procedures and graphical methods]. Messen-steuern-regeln (msr) (in German). 8 (12): 421–425. ISSN 0026-0347. CODEN MSRGAN. [7]

- ^ Kortum, Herbert (1966). "Konstruktion und Minimierung von Halbleiterschaltnetzwerken mittels Graphentransformation". Messen-steuern-regeln (msr) (in German). 9 (1): 9–12. ISSN 0026-0347. CODEN MSRGAN.

- ^ Kortum, Herbert (1966). "Weitere Bemerkungen zur Minimierung von Schaltnetzwerken mittels Graphenmethoden". Messen-steuern-regeln (msr) (in German). 9 (3): 96–102. ISSN 0026-0347. CODEN MSRGAN.

- ^ Kortum, Herbert (1966). "Weitere Bemerkungen zur Behandlung von Schaltnetzwerken mittels Graphen. Konstruktion von vermaschten Netzwerken (Brückenschaltungen)" [Further remarks on treatment of switching networks by means of graphs]. Messen-steuern-regeln (msr) (in German). 9 (5): 151–157. ISSN 0026-0347. CODEN MSRGAN. Kortum, Herbert (1965). "Weitere Bemerkungen zur Behandlung von Schaltnetzwerken mittels Graphen" [Further remarks on treatment of switching networks by means of graphs]. Regelungstechnik (in German). 10 (5): 33–39.

- ^ Kortum, Herbert (1967). "Über zweckmäßige Anpassung der Graphenstruktur diskreter Systeme an vorgegebene Aufgabenstellungen". Messen-steuern-regeln (msr) (in German). 10 (6): 208–211. ISSN 0026-0347. CODEN MSRGAN.

- ^ Kortum, Herbert (1966). "Zur Minimierung von Schaltsystemen" [Minimization of switching circuits]. Wissenschaftliche Zeitschrift der TU Ilmenau (in German). 12 (2): 181–186.

- ^ Tafel, Hans Jörg (1971). "4.3.5. Graphenmethode zur Vereinfachung von Schaltfunktionen". Written at RWTH, Aachen, Germany. Einführung in die digitale Datenverarbeitung [Introduction to digital information processing] (in German). Munich, Germany: Carl Hanser Verlag. pp. 98–105, 107–113. ISBN 978-3-446-10569-0.

Further reading[edit]

- De Micheli, Giovanni (1994). Synthesis and Optimization of Digital Circuits. McGraw-Hill. ISBN 978-0-07-016333-1. (NB. Chapters 7-9 cover combinatorial two-level, combinatorial multi-level, and respectively sequential circuit optimization.)

- Hachtel, Gary D.; Somenzi, Fabio (2006) [1996]. Logic Synthesis and Verification Algorithms. Springer Science & Business Media. ISBN 978-0-387-31005-3.

- Kohavi, Zvi; Jha, Niraj K. (2009). "4–6". Switching and Finite Automata Theory (3rd ed.). Cambridge University Press. ISBN 978-0-521-85748-2.

- Knuth, Donald Ervin (2010). "chapter 7.1.2: Boolean Evaluation". The Art of Computer Programming. 4A. Addison-Wesley. pp. 96–133. ISBN 978-0-201-03804-0.

- Rutenbar, Rob A. Multi-level minimization, Part I: Models & Methods (PDF) (lecture slides). Carnegie Mellon University (CMU). Lecture 7. Archived (PDF) from the original on 2018-01-15. Retrieved 2018-01-15.; Rutenbar, Rob A. Multi-level minimization, Part II: Cube/Cokernel Extract (PDF) (lecture slides). Carnegie Mellon University (CMU). Lecture 8. Archived (PDF) from the original on 2018-01-15. Retrieved 2018-01-15.

- Tomaszewski, Sebastian P.; Celik, Ilgaz U.; Antoniou, George E. (2003). "WWW-based Boolean function minimization" (PDF). International Journal of Applied Mathematics and Computer Science. 13 (part 4): 577–584. Archived (PDF) from the original on 2018-01-15. Retrieved 2018-01-15.